For complete list of my publication, you can visit my google scholar page.

Book Chapter

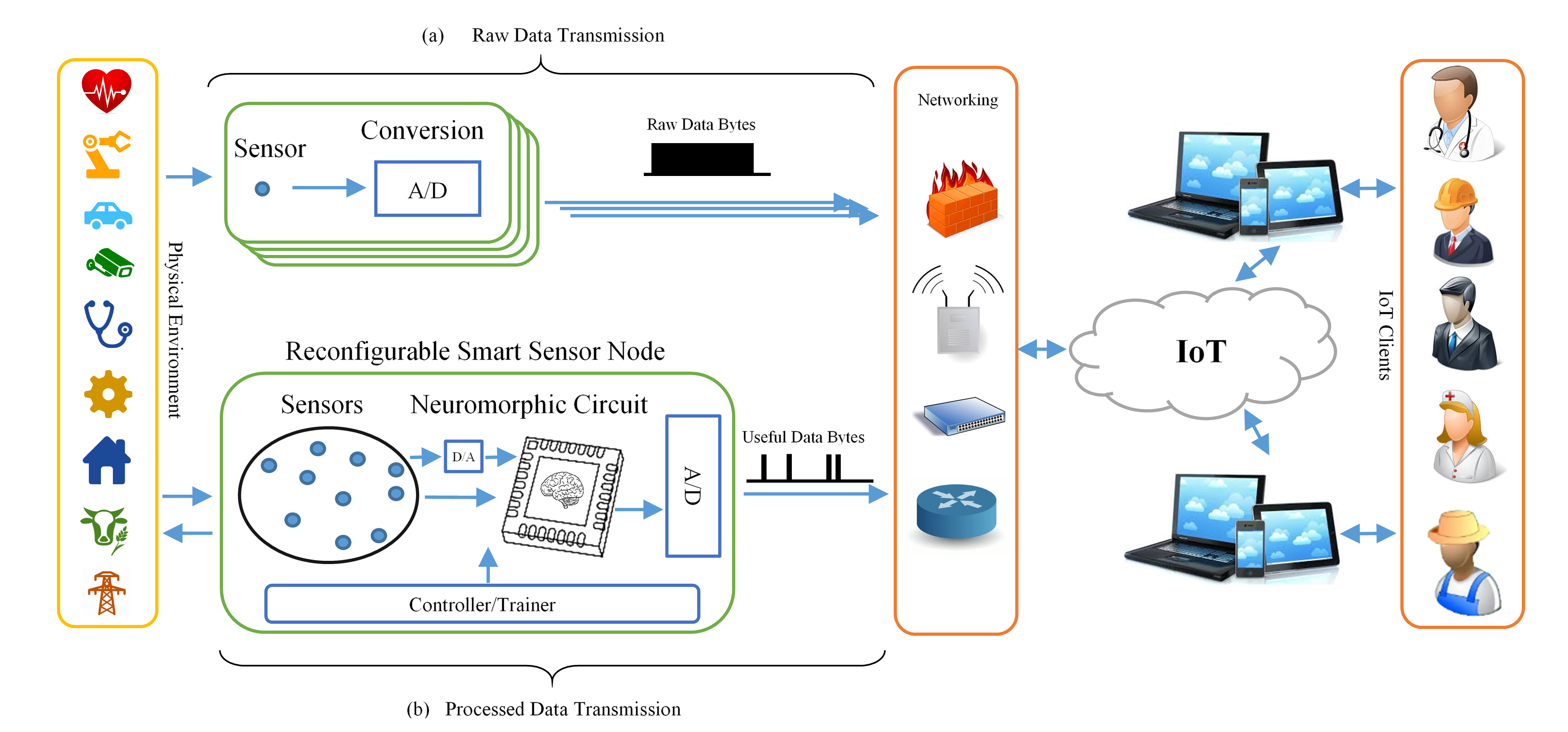

Inverter-based Memristive Neuromorphic Circuit for Ultra-low-power IoT Smart Applications

Arash Fayyazi, Mohammad Ansari, Mehdi Kamal, Ali Afzali-Kusha, Massoud Pedram.

IET Book on Hardware Architectures for Deep Learning. [link]

Peer-Reviewed Journals

OCTAN: An On-Chip Training Algorithm for Memristive Neuromorphic Circuits

Mohammad Ansari, Arash Fayyazi, Mehdi Kamal, Ali Afzali-Kusha, Massoud Pedram.

IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS I), 2019. [link]

SystemVerilog modeling of SFQ and AQFP circuits

Ramy N Tadros, Arash Fayyazi, Massoud Pedram, Peter A Beerel.

IEEE Transactions on Applied Superconductivity, 2019. [link] [Code]

An Ultra-Low-Power Memristive Neuromorphic Circuit for Internet of Things Smart Sensors

Arash Fayyazi, Mohammad Ansari, Mehdi Kamal, Ali Afzali-Kusha, Massoud Pedram.

IEEE internet of things journal, 2018. [PDF]

PHAX: Physical Characteristics Aware Ex-Situ Training Framework for Inverter-Based Memristive Neuromorphic Circuits

Mohammad Ansari, Arash Fayyazi, Ali Banagozar, Mohammad Ali Maleki, Mehdi Kamal, Ali Afzali-Kusha, Massoud Pedram.

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2017. [PDF]

[Code]

Refereed Full-Length Conference Proceedings

SynergicLearning: Neural Network-Based Feature Extraction for Highly-Accurate Hyperdimensional Learning

Mahdi Nazemi, Amirhossein Esmaili, Arash Fayyazi, and Massoud Pedram.

IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2020. [PDF]

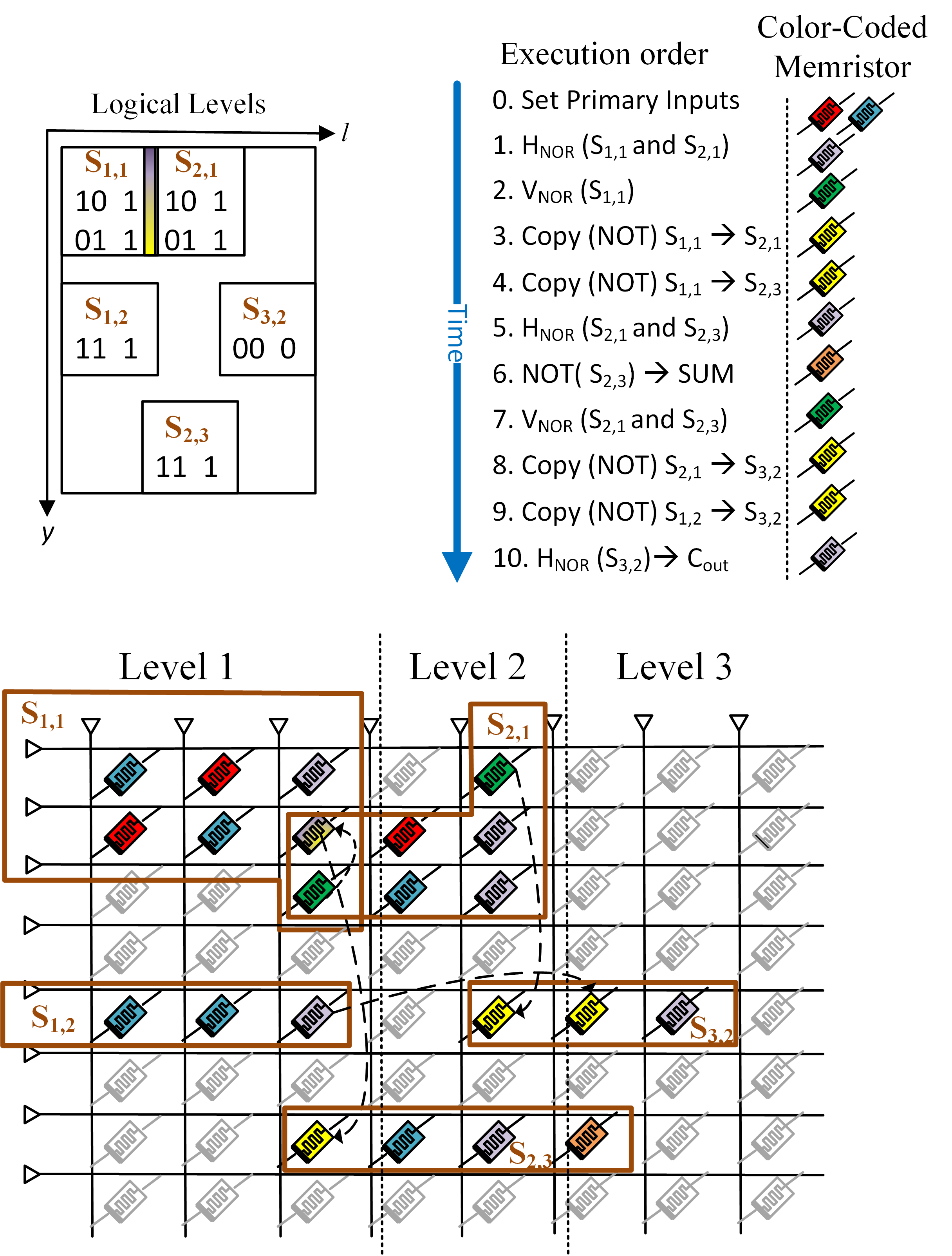

HIPE-MAGIC: A Technology-Aware Synthesis and Mapping Flow for Highly Parallel Execution of Memristor-Aided LoGIC

Arash Fayyazi, Amirhossein Esmaili Dastjerdi, Massoud Pedram.

IEEE/ACM International Symposium on Low Power Electronics and Design (ISLPED), 2020. [PDF]

qCG: A Low-Power Multi-Domain SFQ Logic Design and Verification Framework

Shahin Nazarian, Arash Fayyazi, Massoud Pedram.

IEEE 37th International Conference on Computer Design (ICCD), 2019. [link]

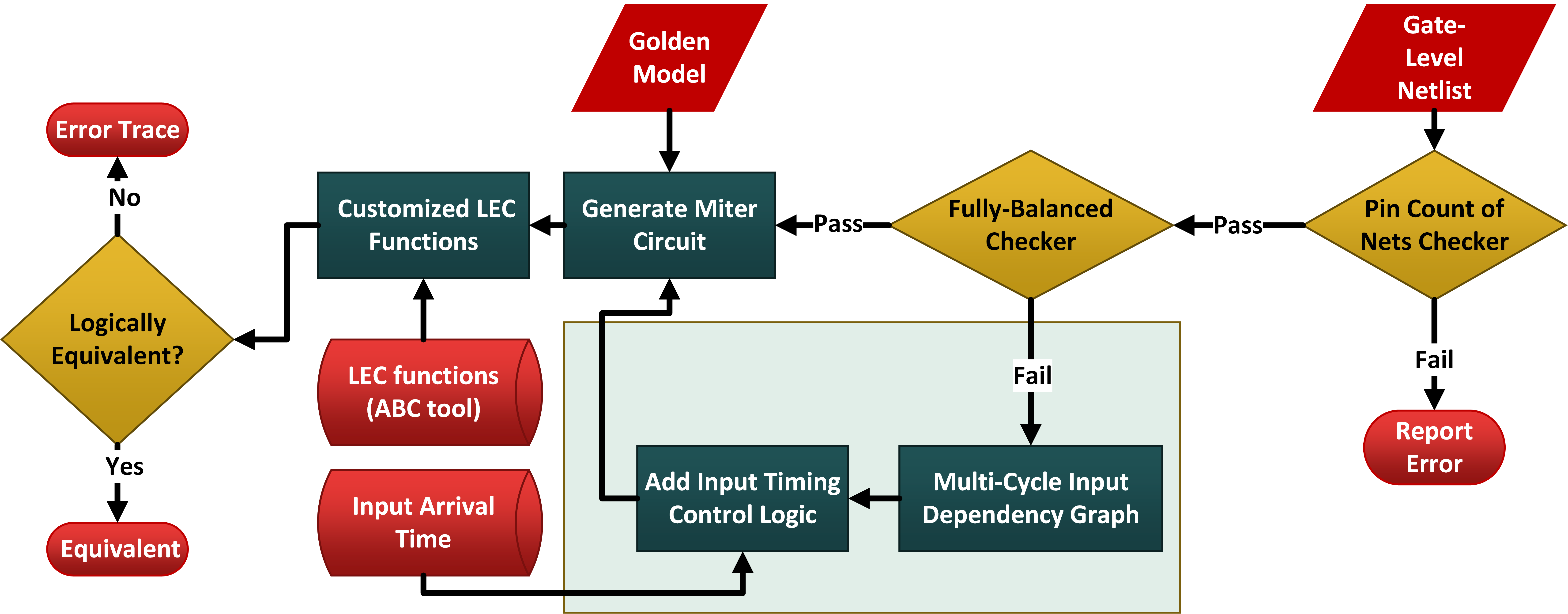

qEC: A Logical Equivalence Checking Framework Targeting SFQ Superconducting Circuits

Arash Fayyazi, Shahin Nazarian, Massoud Pedram.

IEEE International Superconductive Electronics Conference (ISEC), 2019. [link]

CSrram: Area-Efficient Low-Power Ex-Situ Training Framework for Memristive Neuromorphic Circuits Based on Clustered Sparsity

Arash Fayyazi, Souvik Kundu, Shahin Nazarian, Peter A Beerel, Massoud Pedram.

IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 2019. [PDF]

A Hybrid Framework for Functional Verification using Reinforcement Learning and Deep Learning

Karunveer Singh, Rishabh Gupta, Vikram Gupta, Arash Fayyazi, Massoud Pedram, Shahin Nazarian.

ACM Great Lakes Symposium on VLSI (GLSVLSI), 2019. [link]

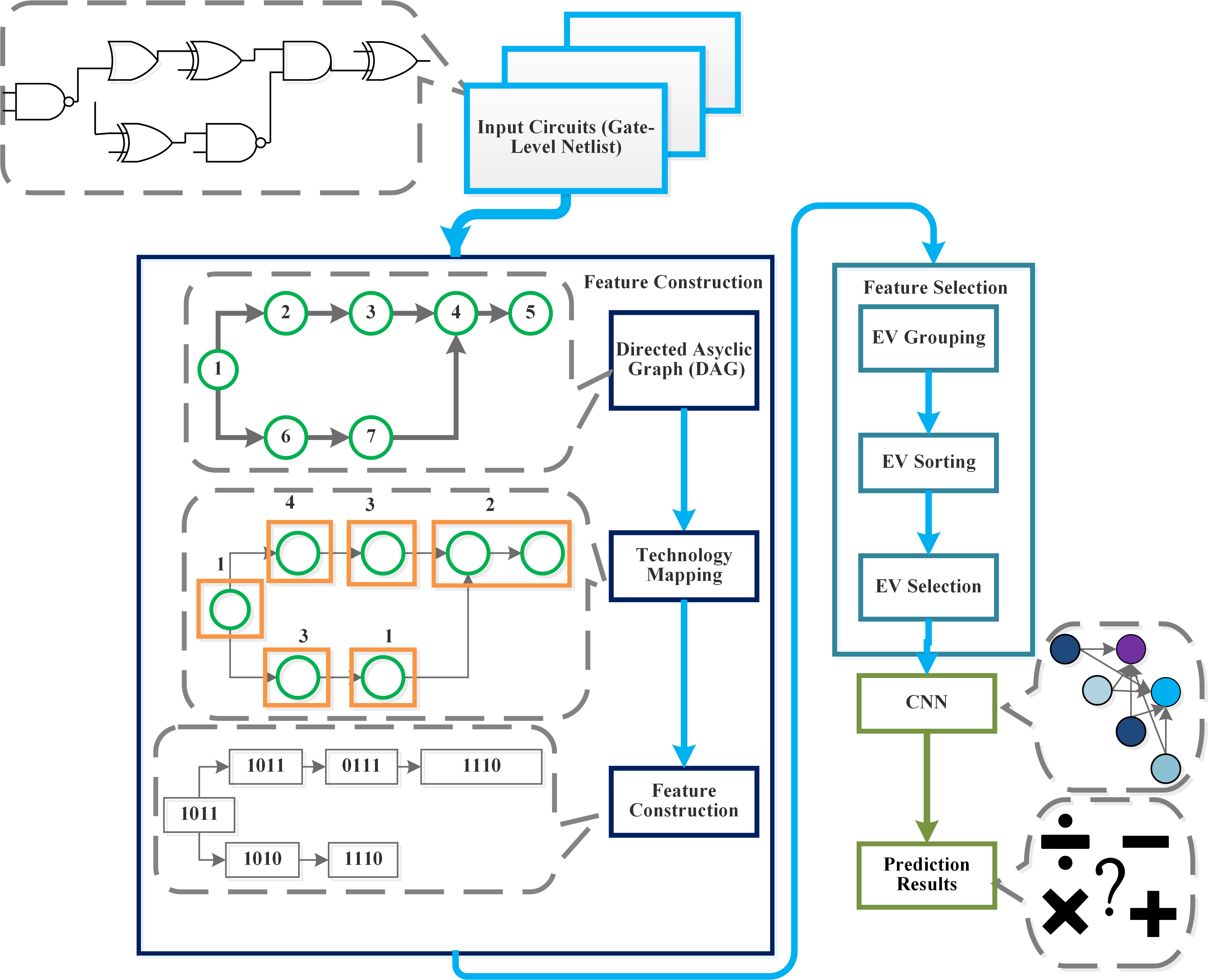

Deep Learning-Based Circuit Recognition Using Sparse Mapping and Level-Dependent Decaying Sum Circuit Representations

Arash Fayyazi, Soheil Shababi, Pierluigi Nuzzo, Shahin Nazarian, Massoud Pedram.

IEEE Design, Automation & Test in Europe Conference & Exhibition (DATE), 2019. [link]

[Code]

[DAC'20 Young Fellow Poster]

[DAC'20 Young Fellow Video]

VeriSFQ: A semi-formal verification framework and benchmark for single flux quantum technology

Alvin D Wong, Kevin Su, Hang Sun, Arash Fayyazi, Massoud Pedram, Shahin Nazarian.

IEEE 20th International Symposium on Quality Electronic Design (ISQED), 2019. [PDF]

SEERAD: A high speed yet energy-efficient rounding-based approximate divider

Reza Zendegani, Mehdi Kamal, Arash Fayyazi, Ali Afzali-Kusha, Saeed Safari, Massoud Pedram.

IEEE Design, Automation & Test in Europe Conference & Exhibition (DATE), 2016. [PDF]