Proposed Framework

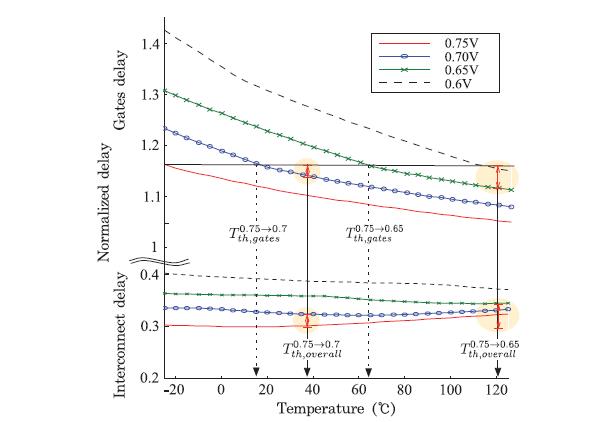

Our studies show that temperature increase makes FinFETs run faster at all supply voltage levels. We refer to this phenomenon as TEI. The following presents the basics of TEI. The delay of a logic gate in a VLSI circuit is directly affected by the driving current (Ion). As Ion increases, the logic gate switches faster and vice versa. For a conventional MOSFET operating at superthreshold Vdd (e.g., 0.9 V), it is well known that as the temperature rises, Ion decreases and that in turn increases the circuit delay. That is why the worst-case timing corner for the commercial MOSFET standard cell library at superthreshold Vdd occurs at the highest temperature (e.g., 125◦C).

Experimental Results

In the previous section, we explained how to exploit the TEI phenomenon to reduce the energy consumption of the circuit while effectively maintaining circuit speed. Interestingly, one recent work exploited the TEI phenomenon to enhance the performance of the multicore processor, whereby increasing frequency of cores while maintaining the voltage level at a certain high temperature point [Cai and Marculescu 2015]. If the circuit is small enough such that the interconnect delay is insignificant, the presented methods in Section 5.1 (and in Cai and Marculescu [2015]) can be directly utilized in the circuit. However, if the interconnect delay takes a substantial portion of the overall circuit delay, which is generally true in large circuits, the interconnect delay should be taken into account to exploit the TEI phenomenon.