Bonus Projects

Different projects have different loads, therefore they have different bonus weights.

Moreover, it is possible that there are unseen obstacles to complete a project and that is why we defined a range for possible bonus points to make sure your effort is fairly evaluated.

Here is the submission link to select your candid projects.

* Special thanks to Zhi-Lio Hurt for advising on the project descriptions.

[1] ISCAS85/89 Benchmarks

- A report of the ISCAS85/89 benchmark by reading the original paper and online resources

- Description of the ISCAS format (.isc) similar to our own SELF format

- Validation of different netlist formats for some of the netlists and converting sequential circuits to combinational alternatives

Requires: Reading and researching online, Verilog simulation, maybe a bit of C++ or Python

[2] Verilog Matching Module

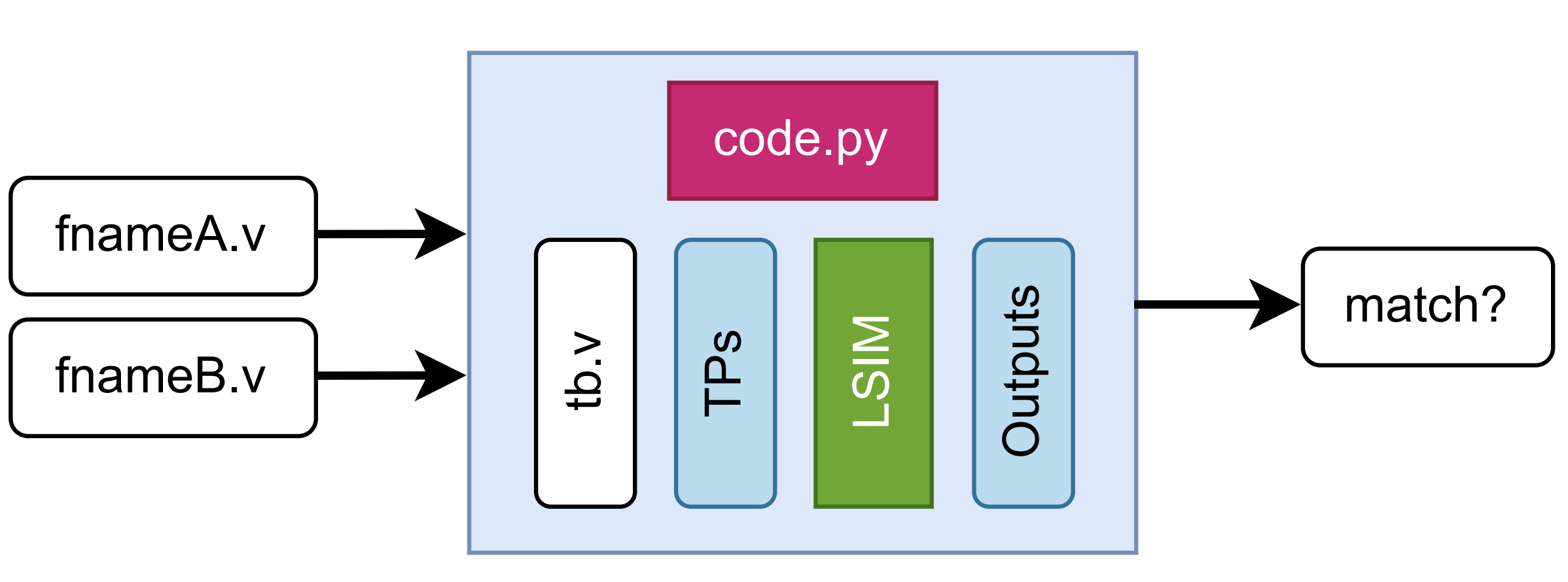

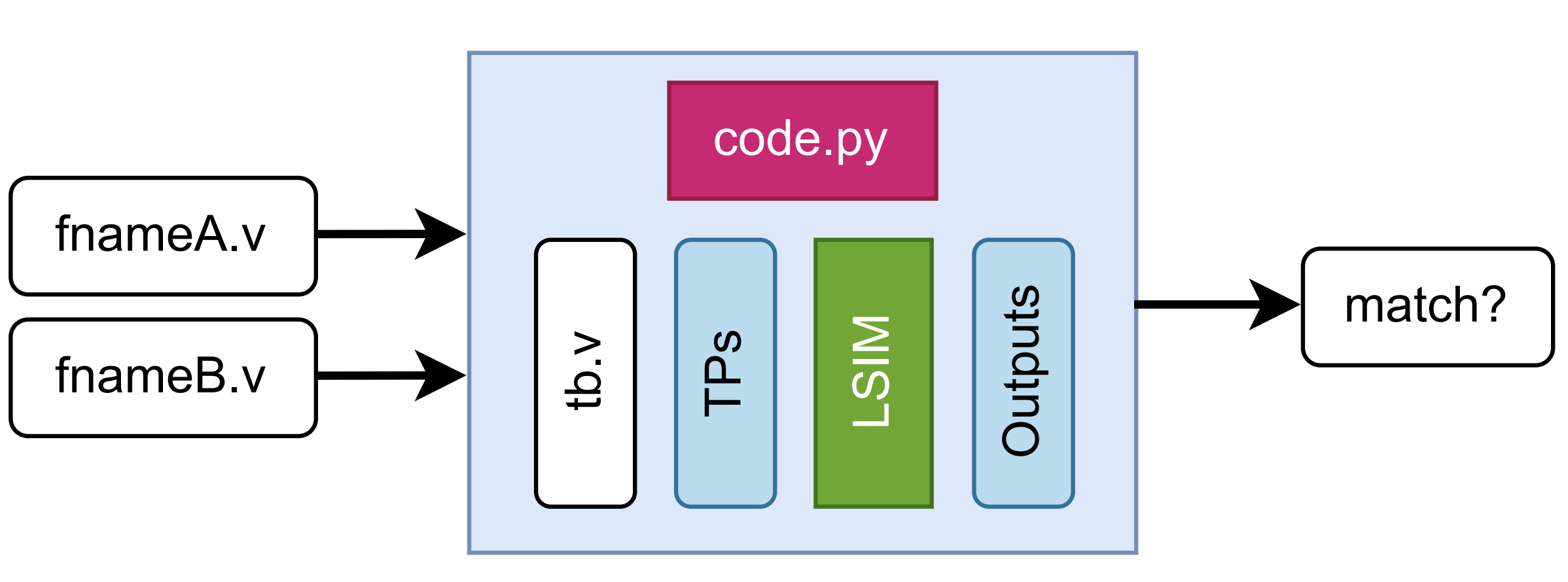

The module is explained below:

- Input: Two (or more) Verilog files

- Output: Showing if the inputs’s functionality match

- Description: We have a number of Verilog files that are supposedly representing the same design, but in different formats, such as flat gate level, hierarchical, structural, and also behavioral. We want to examine if the functionality of these files are the same.

- Process: You need to write down a wrapper (preferably Python) that (1) automatically generates a testbench and a number of test patterns based on the Verilog file (i.e. it’s inputs and outputs) (2) Runs an available logic simulator (take a look into this or ask our lovely Prof. Puvvada) on Verilog files and collecting their output for each tp, and finally (3) comparing the outputs.

Requires: Preferably Python, understanding Verilog simulation

[3] ISCAS85 Circuits’ Description

These 11 circuits were introduced a long time ago (ISCAS85, so in the ISCAS conference of 1985). Each circuit represents a meaningful and well-known design, such as ALU, controller, adder, and multiplier.

There are several items associated with each circuit, and almost all of them are available online.

- Basic description of functionality

- General structural figure

- Bus translation (matching PI/PO)

- Gate-level description in ISCAS, SELF, and Verilog format

- Hierarchical structural model in Verilog

- Hierarchical behavioral model in Verilog

Your job will be creating a report from two of these circuits, making sure all items match each other (for example, their pin assignment should match). In case there are some missing items in each design, we can generate it ourselves.

Requires: Reading and researching online, Verilog simulation, maybe a bit of C++ or Python

[4] 74X-series Benchmark

This benchmark suite has only 4 circuits:

- 74182 : 4-bit carry-lookahead generator

- 74283 : 4-bit adder

- 74181 : 4-bit ALU

- 74L85 : 4-bit magnitude comparator

For this project you need to:

Provide a description of the circuit benchmark.

Provide a description from each circuit, including its functionality.

A report of available formats (ISC, SELF, VERILOG, BENCH), and generating missing formats with available translators. We already have a circuit format translator available.

Drawing the top-level schematic of designs (using automatic tools)

Requires: Reading and researching online, Verilog, maybe a bit of C++ or Python

[5] LGSynth Benchmark

Similar to ISCAS85/89

[6] Netlist Translator

There is an existing in-house Python module that can parse and translate Verilog, ISCAS, and SELF formats to each other. In this project we would like to extend this module to other formats, e.g. BLIF and BENCH.

Requires: Python

[7] PPSF and Fault Detection Probability [Extra Bonus]

In this project you will develop a new fault simulation technique in your simulator which is based on the parallel pattern and single fault (PPSF) scenario. The results of PPSF will then be used (i.e. a few simple formulas) to assign a value to each fault in the circuit representing the difficulty of detecting the fault when using random test patterns. The implementation of this algorithm can also help you with the final version of your simulator.

Requires: C++

by: Mohammad Saeed Abrishami