# **Bounded Algebra and Current-Mode Digital Circuits**

Xunwei Wu

Institute of Cirsuits and Systems, Ningbo University, Ningbo 315211, P.R. China Massoud Pedram Department of Electrical Engineering-System, University of Southern California, CA90089, USA

#### Abstract

This paper proposes two bounded arithmetic operations, which are easily realized with current signals. Based on these two operations, a bounded algebra system suitable for describing current-mode digital circuits is developed and its relationship to the Boolean Algebra, which is suitable for representing voltage-mode digital circuits, is investigated. Design procedure for current-mode circuits using the proposed algebra system is demonstrated on a number of common circuit elements which are used to realize arithmetic operations, such as adders and multipliers.

keywords: Current operation, bounded algebra, current signal, digital circuit

### 1 Explanation of traditional voltage-mode digital circuit design

The basic tasks of digital circuit design are as follows.

(1) Choose a set of basic operations, which meet two requirements: forming a complete set and being easy to transform in order to express and optimize functions.

(2) Determine an electrical entity from voltage, current or charge to represent the logic signal so as to simplify the realization of the basic operations.

(3) Design various electronic devices corresponding to these basic operations, then realize the given logic function by combining these devices according to the corresponding function expression.

Up untill now we always use Boolean algebra to describe the logic function. In the algebra based on comparison lattice, the three basic operations, AND, OR and NOT, can be re-defined as follows:<sup>[1]</sup>

| AND (minimum operation) | $x \cdot y \cdot z = \min(x, y, z) \tag{(1)}$ | 1) |

|-------------------------|-----------------------------------------------|----|

|                         |                                               |    |

AND (minimum operation) $x \cdot y \cdot z = \min(x, y, z)$ OR (maximum operation) $x + y + z = \max(x, y, z)$ (2)

| NOT (threshold comparison) | $\overline{x} = \begin{cases} 0, \\ \end{array}$ | if $x > 0.5$ ; | (3) |

|----------------------------|--------------------------------------------------|----------------|-----|

| (uneshold comparison)      | x = 1,                                           | if $x < 0.5$ . | (3) |

In Eq.(3) the detection threshold for signal x is represented by 0.5, which is set in the middle of the two logic levels, 1 and 0. The definition of  $\overline{x}$  shows that  $\overline{x} = 0$  when x > 0.5 (i.e. x = 1), and  $\overline{x} = 1$ when x < 0.5 (i.e. x = 0). According to the above definitions all three basic operations in Boolean algebra are related to comparison operation.

It is well known that AND, OR and NOT form a complete set to express arbitrary functions. For example, a function with two inputs can be expressed by the general tabular form as shown in Table 1, where  $c_i \in \{0,1\}$ . By using these basic operations f(x,y) can be expressed by the following canonical expansion form:

$$f(x, y) = c_0 \cdot (\overline{x} \cdot \overline{y}) + c_1 \cdot (\overline{x} \cdot y) + c_2 \cdot (x \cdot \overline{y}) + c_3 \cdot (x \cdot y)$$

(4)

Actually, the above equation describes the procedure to look up Table 1 by using algebraic language. For instance, the first term  $c_0 \cdot (\overline{x} \cdot \overline{y})$  in Eq.(4) represents that when x = 0 and y = 0 the function

Project supported by NNSF(No.69573008) of China and NSF Grant (No.53-4503-2694) of USA.

value is checked out as  $c_0$ , etc.

| uU | ie i. Tubului e |   | ilput logie fulleti   |

|----|-----------------|---|-----------------------|

| -  | x               | у | f(x,y)                |

| -  | 0               | 0 | $c_0$                 |

|    | 0               | 1 | $c_1$                 |

|    | 1               | 0 | $c_2$                 |

|    | 1               | 1 | <i>C</i> <sub>3</sub> |

Table 1. Tabular expression of 2-input logic function

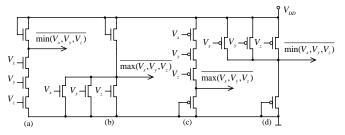

In the traditional design of digital circuits, voltage is used to represent the logic signal since the voltage signals can easily realize the comparison operations. For example, in bipolar circuits<sup>[2]</sup> AND (minimum) and OR (maximum) operations among voltage signals can be realized by pn junction's forward characteristics. On the other hand, in MOS circuits minimum (AND) or maximum (OR) operations among voltage signals can be realized by connecting transistors in series or in parallel, as shown in Fig.1. For instance, the minimum voltage among inputs in Fig.1(a) determines the conduction condition of the series-connected nMOS structure. If  $\min(V_x, V_y, V_z)$  is high level (i.e. all inputs are high) the structure will be conductive and the output will be low. (For simplicity, we denote the output by  $\min(V_x, V_y, V_z)$  in Fig.1(a)). Instead, the maximum voltage among  $V_x$ ,  $V_y$  and  $V_z$ determines the conduction condition of the parallel-connected nMOS structure. Obviously, NAND/NOR operations in nMOS circuits are realized based on the structures in Fig.1.(a) and (b), and NOR/ NAND operations in pMOS circuits are realized based on the structures in Fig.1.(c) and (d) (if the positive logic convention is adopted). Besides, combining Fig.1.(a) and 1.(d) will form a NAND gate and combining Fig.1.(b) and 1.(c) will form a NOR gate in CMOS circuits. As to the NOT (threshold comparison) operation, it is realized by comparing the input signal with the inherent threshold voltage of MOS transistors.

Fig. 1 Comparison of voltage signals by MOS connection

In the previous paragraph, we explained the traditional design of digital circuits by using Boolean algebra and voltage levels. We can now understand why current are seldom used to represent logic signal since it is difficult to compare and select the minimum or maximum among current signals. In the following, we will introduce another kind of operations, which are easy to realize with current signals, and introduce a corresponding algebra for developing the current-mode circuits. This is the main contribution of the present paper.

### **2** Bounded algebra suitable for current-mode signals

Current is easy to add or subtract by connecting current sources to each other. This indicates to us that if addition (&) and subtraction (–) are introduced as the basic operations their realization based on current signal will be easy. However, the conventional arithmetic addition x & y and subtraction x - y couldn't be used directly due to complications that 1 & 1 = 2 and 0 - 1 = -1. Instead, we introduce the following two bounded arithmetic operations:

Bounded addition

$$x \biguplus y = \min(1, x \& y) = \begin{cases} 1, & \text{if } x \& y > 1; \\ x \& y, & \text{otherwise.} \end{cases}$$

(5)

Bounded subtraction

$$x\Theta y = \max(0, x - y) = \begin{cases} 0, & \text{if } x - y < 0; \\ x - y, & \text{otherwise.} \end{cases}$$

(6)

We can prove that two bounded operations may be expressed with traditional Boolean operation, AND, OR and NOT, as follows.

$$x \biguplus y = x + y \tag{7}$$

$$x\Theta y = x \cdot \overline{y} \tag{8}$$

If x = 1 in Eq.(8) we can obtain NOT operation:

$$1\Theta y = \overline{y} \tag{9}$$

Since OR and NOT form a complete set, therefore, the two bounded operation also form a complete set. In fact the bounded subtraction can form a complete set by itself since  $(1\Theta x)\Theta y = \overline{x} \cdot \overline{y} = \overline{x+y}$  and NOR forms a complete set. In the next section we will find that the bounded subtraction plays an important role in the design of current-mode circuits.

By using two bounded operations we can express the 2-input functions in Table 1 by the following canonical expansion:

$$f(x, y) = [c_0 \Theta(x \sqcup y)] \sqcup [c_1 \Theta(x \sqcup \overline{y})] \sqcup [c_2 \Theta(\overline{x} \sqcup y)] \sqcup [c_3 \Theta(\overline{x} \sqcup \overline{y})]$$

(10)

Similarly, the above equation describes the procedure to look up Table 1 by using algebraic expressions. For instance, the first term  $c_0 \Theta(x \burdle y)$  in Eq.(10) represents that when x = 0 and y = 0 the function value is checked out as  $c_0$ , etc. In fact, from Eqs.(7) and (8) we have  $c_0 \Theta(x \burdle y) = c_0 \cdot \overline{x} + \overline{y} = c_0 \cdot \overline{x} \cdot \overline{y}$ . Since the OR operation (+) is equivalent to the bounded addition ( $\burdle y$ ) Eq.(10) is converted into form of Eq.(4).

Based on the above definitions and relationships with Boolean operations, we can derive the following properties for two bounded operations:

$$\begin{array}{ll} 0 \ \forall x = x, & 1 \ \forall x = 1, & x \ \forall x = x, & x \ \forall \overline{x} = 1; \\ 0 \ \Theta x = 0, & 1 \ \Theta x = \overline{x}, & x \ \Theta 0 = x, & x \ \Theta 1 = 0, & x \ \Theta x = 0, & x \ \Theta \overline{x} = x \end{array}$$

Also it may be verified that the above bounded operations have the similar properties with general arithmetic operations, such as:

$$x \biguplus y = y \biguplus x$$

(x \U03cm y) \U2 = x \U(y \U2) = x \U32cm y \U2

x\O(y \U2) = (x\Oy) \OZ

We should point out that the signal value obtained by the conventional arithmetic addition is restrained by bounding operation with an upper bound 1. In fact, the upper bound may be set to a value d larger than 1, resulting in non-binary signal values. The advantage is that the high valued signal may lead to a simpler function expression and thus a simpler circuit structure. Therefore the

bounded addition operation in Eq.(5) can be modified as

$$x \biguplus_{d} y = \min(d, x \& y) = \begin{cases} d, & \text{if } x \& y > d; \\ x \& y, & \text{otherwise.} \end{cases}$$

(11)

where *d* is a positive integer. If needed the arithmetic addition & can be directly used for forming an intermediate signal with high value in function expression. As an example, the 3-variable AND and NOR function can be expressed by using the sum signal  $\Sigma = x \& y \& z, \Sigma \in \{0, 1, 2, 3\}$ , as follows:

$$x \cdot y \cdot z = \Sigma \Theta 2 \tag{12}$$

$$x + y + z = 1\Theta\Sigma \tag{13}$$

The above two expressions can be easily verified by using the Karnaugh Map shown in Fig.2.

| X                              | <sup>z</sup> 00 | 01 | 11 | 10 | x                          | z 00 | 01 | 11 | 10                         | x  | z 00 | 01 | 11 | 10 |

|--------------------------------|-----------------|----|----|----|----------------------------|------|----|----|----------------------------|----|------|----|----|----|

| 0                              | 0               | 0  | 0  | 0  | 0                          | 1    | 0  | 0  | 0                          | 0  | 0    | 1  | 2  | 1  |

| 1                              | 0               | 0  | 1  | 0  | 1                          | 0    | 0  | 0  | 0                          | 1  | 1    | 2  | 3  | 2  |

|                                | (a) (b)         |    |    |    |                            |      |    |    |                            | (c | :)   |    |    |    |

| Fig. 2 (a) $x \cdot y \cdot z$ |                 |    |    |    | (b) $\overline{x + y + z}$ |      |    |    | (c) $\Sigma = x \& y \& z$ |    |      |    | z  |    |

Since the bounded operations are derived from the general arithmetic addition and subtraction, they have simple relationships with traditional Boolean operations. A mediate algebra between arithmetic and Boolean algebra is thus formed.

# **3** Characteristic of current signals and design of current-mode circuits

CMOS or bipolar technology can be used to illustrate the design of current-mode circuits.  $I^2L$  is the current-mode circuit in bipolar technology<sup>[3-5]</sup>. In this paper only the current-mode circuit in CMOS technology will be discussed since it is receiving increasing attention in recent years<sup>[6-10]</sup>.

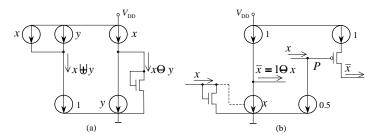

The circuit realizations of the two bounded operations are shown in Fig.3(a). In the left part the current flowing through the connection node cannot be larger than 1, therefore, the bounded addition is realized. On the other hand, in the right part the current flowing through the connection node cannot be less than 0, then the bounded subtraction is realized. Notice that its load is an nMOS current mirror. In the following we show examples of building current-mode digital circuits.

#### (1) Inverter

From Eq.(9) we can obtain a simple circuit realization shown in the left part of Fig.3(b), where only two nMOS transistors (for the current mirror) and one pMOS transistor (for forming the current source 1) are used. The dotted line in the circuit is used to express the control of a current mirror. The shortcoming of this realization is lack of level-restoration. However, based on Eq.(3) we can design an inverter with level-restoration function, as shown in the right part of Fig.3(b). Here node *P* assumes a high level, nMOS transistor turns off and output current is 0 when x = 1 (i.e. x > 0.5); Similarly node *P* assumes low level, pMOS transistor turns on and output current is 1 when x = 0 (i.e. x < 0.5). In Fig.3(b) two pMOS transistors and one nMOS transistor are needed. One of pMOS transistors is used to switch the unit current source.

Fig. 3 (a) Circuit realization of bounded operations (b) Current-mode inverter

(2) Boolean logic gates

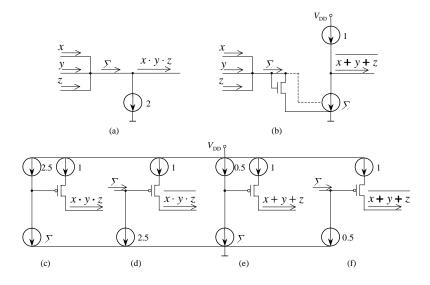

From Eqs.(12) and (13), the simple AND and NOR gates without level-restoration function are shown in Fig.4(a) and (b), where the intermediate sum signal  $\Sigma = x \& y \& z$  is used. Instead, we can derive the following switching expressions from Karnaugh Map in Fig.2:

$$\begin{aligned} x \cdot y \cdot z &= \begin{cases} 0, & \text{if } \Sigma < 2.5; \\ 1, & \text{if } \Sigma > 2.5. \end{cases} \\ \hline x \cdot y \cdot z &= \begin{cases} 0, & \text{if } \Sigma > 2.5; \\ 1, & \text{if } \Sigma > 2.5; \\ 1, & \text{if } \Sigma < 2.5. \end{cases} \\ x + y + z &= \begin{cases} 0, & \text{if } \Sigma < 0.5; \\ 1, & \text{if } \Sigma > 0.5. \end{cases} \\ \hline x + y + z &= \begin{cases} 0, & \text{if } \Sigma > 0.5; \\ 1, & \text{if } \Sigma > 0.5; \end{cases} \\ \hline x + y + z &= \begin{cases} 0, & \text{if } \Sigma > 0.5; \\ 1, & \text{if } \Sigma > 0.5; \end{cases} \end{aligned}$$

The corresponding current-mode Boolean gates with restoration function are shown in Fig.4(c), (d), (e) and (f).

Fig. 4 Current-mode Boolean gates (a) simple AND gate (b) simple NOR gate (c) AND gate (d) NAND gate (e) OR gate (g) NOR gate

#### (3) Arithmetic circuits

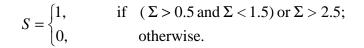

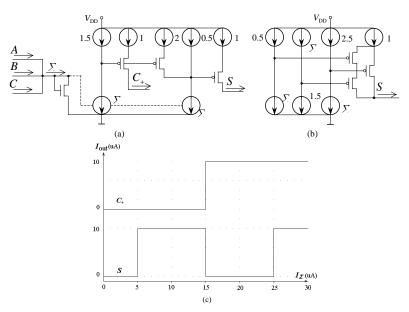

Since currents are easy to add or subtract, the current-mode circuit is most suitable for realizing arithmetic circuits such as adders and multipliers. Taking the full adder with three inputs (*A*, *B*, *C*) and two outputs (carry-out  $C_+$  and sum *S*) as the example, we can obtain Table 2 by using the intermediate sum signal  $\Sigma = x \& y \& z$  and derive the following switching expressions for  $C_+$  and *S*:

| $C_{+} = \begin{cases} 0\\ 1 \end{cases}$ | ),<br>, |         | $\Sigma < \Sigma >$ |      | ·                  |

|-------------------------------------------|---------|---------|---------------------|------|--------------------|

| $S = \begin{cases} 0, \\ 1, \end{cases}$  |         |         |                     |      | & 0.5);<br>& 0.5). |

| Tabl                                      | e 2.    | Truthta | ble of a            | full | adder              |

| Σ                                         | 0       | 1       |                     | 2    | 3                  |

| $C_+$                                     | 0       | (       | )                   | 1    | 1                  |

| S                                         | 0       | 1       | l                   | 0    | 1                  |

Notice that in the function *S* the switching threshold is controlled by carry-out  $C_+$ . The corresponding circuit realizations are shown in Fig.5(a), where three nMOS transistors are used for forming the current mirror of  $\Sigma$ , five pMOS transistors with various widths are used for generating the five current sources (1.5, 1, 2, 0.5, 1), and other three pMOS transistors are used as switches. Therefore, a total of 11 MOS transistors are needed for the current-mode full adder. In contrast, the voltage-mode full adder needs 28 MOS transistors for a full complementary MOS realization<sup>[111]</sup>. If we do not use  $C_+$  to control switch threshold in design we can derive *S* directly from its truthtable given in Table 2:

Fig. 5 Current-mode full adder and its DC transfer characteristics

The design corresponding to the above switching expression is shown in Fig.5(b). PSPICE has been used to simulate the circuit in Fig.5(a) with 1 $\mu$ m CMOS technology. The currents corresponding to logic level 0, 1, 2, 3 are 0, 10 $\mu$ A, 20 $\mu$ A and 30 $\mu$ A, respectively. The DC transfer characteristics of the

circuit is given in Fig.5(c). It is shown that the circuit has ideal logic function with precise detective threshold currents corresponding to 0.5 ( $5\mu$ A), 1.5 ( $15\mu$ A) and 2.5 ( $25\mu$ A).

In fact the higher the number of signals which are added together, the higher the area advantage of current-mode circuits. For example, four adders will be needed to realize addition of seven binary signals in voltage-mode design, as shown in Fig.6(a). This realization needs 112 transistors. However, in current-mode design, we can derive the following expressions from the truthtable shown in Table 3:

$$\begin{split} y_2 &= \begin{cases} 0, & \text{if } \Sigma < 3.5; \\ 1, & \text{if } \Sigma > 3.5. \end{cases} \\ y_1 &= \begin{cases} 0, & \text{if } \Sigma < (4y_2 \& 1.5); \\ 1, & \text{if } \Sigma > (4y_2 \& 1.5). \end{cases} \\ y_0 &= \begin{cases} 0, & \text{if } \Sigma < (4y_2 \& 2y_1 \& 0.5); \\ 1, & \text{if } \Sigma > (4y_2 \& 2y_1 \& 0.5); \end{cases} \end{split}$$

The circuit corresponding to the above expressions is shown in Fig.6(b), where only 19 MOS transistors are used. It is thus evident that devices and interconnections will are significantly reduced in arithmetic circuits, such as adder and multiplier, if current-mode design are used. The most convincing demonstration of the advantages of current-mode CMOS design is a 32×32 multiplier presented<sup>[6]</sup>. This  $32 \times 32$  multiplier chip is half the size of an equivalent voltage-mode CMOS realization, dissipates half the power, and has a multiply time within 5% of the fastest reported multiply time of a comparable design of that era.

0 4 6 0 0 0 0 1 1 1 **y**<sub>2</sub> 0 0 1 1 0 0 1 y1 0 1 0 1 0 1 0 ٧n FΑ (b) (a)

Truthtable of a seven binary signals Table 3.

Fig. 6 Adder of seven binary signals (a) voltage-mode (b) current-mode

The circuit corresponding to the above expressions is shown in Fig.6(b), where only 19 MOS transistors are used. It is thus evident that devices and interconnections will are significantly reduced in arithmetic circuits, such as adder and multiplier, if current-mode design are used. The most convincing demonstration of the advantages of current-mode CMOS design is a  $32 \times 32$  multiplier presented<sup>[6]</sup>. This  $32 \times 32$  multiplier chip is half the size of an equivalent voltage-mode CMOS realization, dissipates half the power, and has a multiply time within 5% of the fastest reported multiply time of a comparable design of that era.

# 4 Conclusions

This paper showed that the choice of algebra system used for designing digital circuits is dependent on which electrical entity is used to represent the logic signal in circuits. If the voltage signal is used, the Boolean algebra based on comparison lattice is a better choice. However, if the current signal is used, comparison operations in Boolean algebra are not easy to realize. Since addition or subtraction operations can be easily realized by connecting wires together, we introduced bounded arithmetic operations as the basic operations and formed a corresponding bounded algebra suitable for the design of current-mode circuits. The design procedure of the current-mode circuits was demonstrated for some typical circuits. It was shown that the proposed bounded operations and the corresponding algebra system are very effective for designing current-mode circuits. In addition to the design flexibility, the arithmetic circuits, such as adders and multipliers, have simple structure in current-mode realization. In the end, as the charge signal and current signal are all easy to be added, we should point out that the bounded algebra can be spreaded into charge circuits, such as CCD.<sup>[12]</sup>

### References

- [1] Wu, X. and Hang, G. Switching circuits based on comparison operations and multiple- $\beta$  transistor, *Science in China (Series E)*, 1997, 27(4): 353~361.

- [2] Wang S., Wu, X. and Feng, H., The high speed ternary logic gates based on the multiple-b transistors, In *IEEE Proc. of Int'l. Symp. on Multiple Valued Logic*, Bloomington, 1995, 178-181.

- [3] Dao, T. T., Threshold I<sup>2</sup>L and its application to binary symmetric functions and multivalued logic, *IEEE J. Solid State Circuits*, 1977, 12(5): 463-472.

- [4] Wu, X. and Chen, X., The synthesis of ternary functions under fixed polarities and ternary I<sup>2</sup>L circuits, In *IEEE Proc. of Int'l. Symp. on Multiple Valued Logic*, Kyoto, 1983, 424-429.

- [5] Wu, X. and Deng, X., Design of ternary I<sup>2</sup>L circuits based on ternary grounded current switches, in *IEEE Proc. of China Int. Conf. on Circuits and Systems*, 1991, 936~939.

- [6] Kawahito, S., Kameyama, M., Higuchi, T. and Yamada, H., A 32×32 bit multiplier using multiple-valued MOS current-mode circuits, *IEEE J. Solid State Circuits*, 1988, 23(1): 124-132.

- [7] Peyalo, F. J. et al., CMOS current-mode multiple-valued PLA's, *IEEE Transactions on Circuits and Systems*, 1991, 38(4): 434-441.

- [8] Current, K. W., Algorithmic of analogue-to-quaternary converter circuit using current-mode CMOS, *Electronic Lett.*, 1992, 28(12): 1111-1112.

- [9] Wu, X. and Deng, X., Design of ternary current-mode CMOS circuits based on switch-signal theory, *Journal of Electronics*, 1993, 10(3): 193-202.

- [10] Current, K. W., Current-mode CMOS multiple-valued logic circuits, *IEEE J. Solid State Circuits*, 1994, 29(2): 95-107.

- [11] Weste, N. H. E. and Eshraghian, K., Principles of CMOS VLSI Design: A Systems Perspective, 2nd Edition, Addison-Wesly Publishing Company, New York, 1993.

- [12] Wu, X. and Pedram, M., Design of ternary CCD circuits referring to current-mode CMOS circuits, In *IEEE Proc.* of *ISMVL*, Antigonish, 1997, 209-214.

**Wu Xunwei** graduated from Physics Department, Hangzhou University in 1962. Now he is a Professor in the Department of Electronic Engineering, Zhejiang University and a Supervisor for Ph. D. candidates. He is the author of the book entitled "Design Principles of Multivalued Logic Circuits" and more than two hundred papers. Prof. Wu is a Senior Member of IEEE and the Vice-Director of MVL & FL Society, the Chinese Computer Federation. His main research interests include multivalued logic circuits and systems, digital circuits design at switch level and low power digital circuits.

**Massoud Pedram** received the BS degree in Electrical Engineering from California Institute of Technology and MS and Ph.D. degrees in Electrical Engineering and Computer Sciences from the University of California, Berkeley in 1989 and 1991. respectively. He then joined the Department of Electrical Engineering Systems at the University of Southern California where he is currently an associate professor. Prof. Pedram is the author of two books and more than one hundred papers. He has been the committeeman of IEEE DAC program committee since 1992, and he is one of the founders of International symposium on Low Power Design. He is a Member of IEEE Circuits and Systems Society and ACM - SIGDA. His research interests include logic synthesis, computer-aided design of VLSI circuits and systems and low power VLSI design.